本内容承接上文。

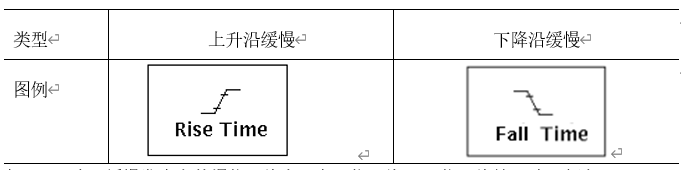

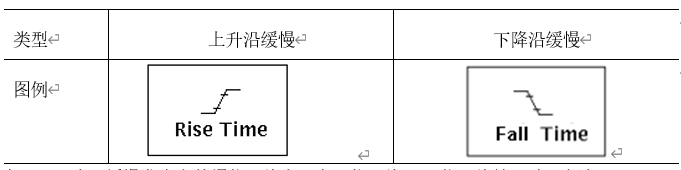

1) 信号边沿缓慢

危害:上升、下降沿缓慢发生在数据信号线上(串口信号线,HW信号线等)时,会造成数据采样错误。

产生原因:驱动能力不够,或者负载过大(例如链路阻抗太大)

解决建议:

n 提高驱动能力;

n 减小负载。

注意:由于驱动不足或者负载过大,信号边沿缓慢常常伴随着信号幅度较低现象。

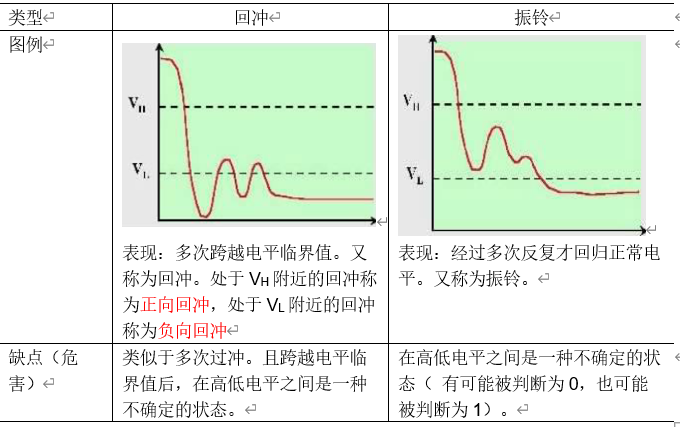

4)振荡(回冲/振铃)

产生原因:匹配不当(例如匹配阻抗过大、过小)。

解决方式:更改为合适的匹配电阻/阻抗。

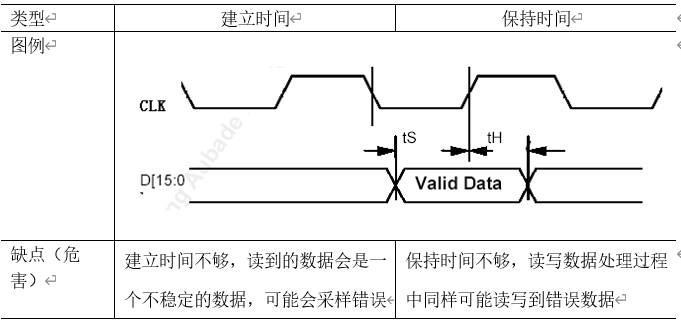

5)建立、保持时间(Setup time & Hold time)

建立保持时间是一个时序的概念。通常把单板的数字信号分为控制信号、时钟信号、地址信号、数据信号等,

时序关系就是这些信号间的相互关系。判断时序关系主要有两个指标:建立时间和保持时间。

如下图,建立时间就是指在触发器的采样信号(这个采样信号通常是指时钟)有效之前,数据已经稳定不变的时间;而保持时间是指采样信号有效之后数据保持稳定不变的时间。

产生原因:设计时没有考虑清楚,设计出错。或者没有考虑到设计容限范围,在某些异常情况下(例如温度变化使得器件参数漂移)建立、保持时间不够。

解决建议:

n 设计时把时钟从FPGA/CPLD中引出,在设计裕度不够时可以调节;

n 对于时钟边沿采样信号,尽量使得采样时钟边沿在数据的中间,这样尽管器件参数漂移,设计上还是有较大的裕度。

注意:

n 在某些特殊情况下,建立时间和保持时间的值可以为零;

n 有时芯片资料给出的参数不对,按照手册要求设计反而出错(这在自己开发ASIC的情况下可能会发生。商用芯片一般不存在此类问题)。

看了上面两篇介绍,其实很多信号问题都是由于阻抗不匹配引起的,出线带不动或者过冲等问题,因此在电路设计中要认真查看数据手册,尽量使用厂家提供的范例电路,但是范例电路也不能完全保证器件正常工作,因此也要根据功能电路和芯片进行仿真和阻抗计算。