在电路设计中,除了器件选择和电路设计外,良好的PCB设计也是影响系统EMC性能的重要因素。由于PCB是系统的固有组成部分,因此通过PCB技术来提高系统的EMC性能并不会带来额外的成本。

需要注意的是在PCB设计中,并没有严格规定的需要绝对遵守的规则,没有哪一条规则适用于所有的PCB设计。大多数PCB设计受电路板尺寸和层数的限制,一些规则可能适用于,但另一些规则可能就不适用,大部分规则的使用取决于PCB设计者的经验。但是在PCB设计中,还是有一些通用的规则,本文讨论的就是这些技术。

PCB的基本参数

一块PCB板是由一系列的铜皮、走线以及树脂层叠加而成。PCB上的走线具有电阻、电容和电感三种参数。

(1)电阻:走线的电阻由走线的高度和横截面积决定。

(2)电容:走线的电容由介质、面积和走线之间的距离决定。

(3)电感:走线的电感沿走线均匀分布,大概为1Nh/m。

对于一条高度1oz、宽度0.5mm、长度20mm、与地平面间为0.25mm FR4介质的走线来说,它的电特性参数为9.8mΩ电阻、20nH电感以及相对于地平面为1.66pF电容。

上面这些参数与器件的寄生参数相比可以忽略不计,但是PCB板上所有走线的参数累加起来就可能超过器件的寄生参数。所以,设计者需要遵循以下规则:

(1)增加走线间的距离,这可以减少走线间的容性串扰。

(2)电源线和地线平行放置,增大电源和地之间的电容。

(3)敏感和高频率走线要远离携带高噪声信号的电源走线。

(4)加宽电源线和地线的走线宽度,减少电源线和地线的阻抗。

分割技术

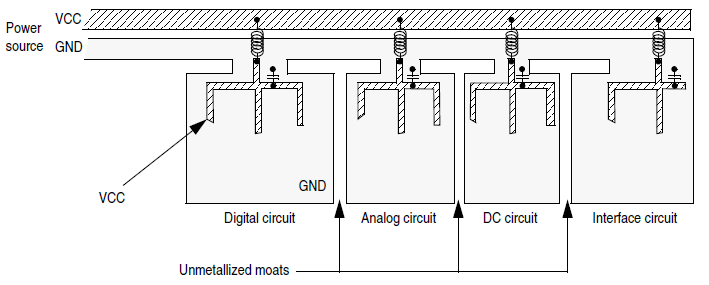

分割就是不同类型电路之间的物理隔离,减少电路之间的耦合。

如上图所示为不同类型电路之间的分割示意图。

集成电路去耦

电路局部去耦可以减少噪声沿着电源路径传播。在PCB的电源入口放置大的旁路电容可以帮助减少电源纹波,并可以满足突发的电源电流需求。另外,在每个集成电路的电源和地之间应放置去耦电容,并且要尽可能靠近电源和地引脚,这可以减少集成电路的开关噪声沿着电源线和地线传播。

参考平面中的RF电流

不管在多层板的地平面中还是单层板的地线中,总会存在从负载到电源的回流路径。回流路径的阻抗越小,PCB板的EMC性能越好。长的回流路径会导致不同电路之间的耦合,因此回流路径越短越好,回流面积越小越好。

走线隔离

走线隔离可以减小同一层中走线的串扰和噪声耦合。走线要遵守3W规则,如下图所示。为了进一步减小磁场耦合,在关键信号线周围要放置地线减少噪声信号的耦合。

保护和分流走线

在时钟电路中,局部去耦电容可以减少噪声沿着电源线传播。但是,时钟信号线也需要采取保护措施,以免受到其它EMI噪声的影响,否则会导致时钟抖动现象。

保护和分流走线是隔离系统中关键信号线的有效手段,如上图所示,它们在PCB中与被保护信号线平行放置。它们不仅隔离从其它信号线过来的噪声信号,也阻止本地噪声耦合到其它走线。

保护走线和分流走线的区别就是分流走线不需要端接(连接到地),但保护走线需要在两端都要接地。